AMD Launches Excavator on Desktop: The 65W Athlon X4 845 for $70

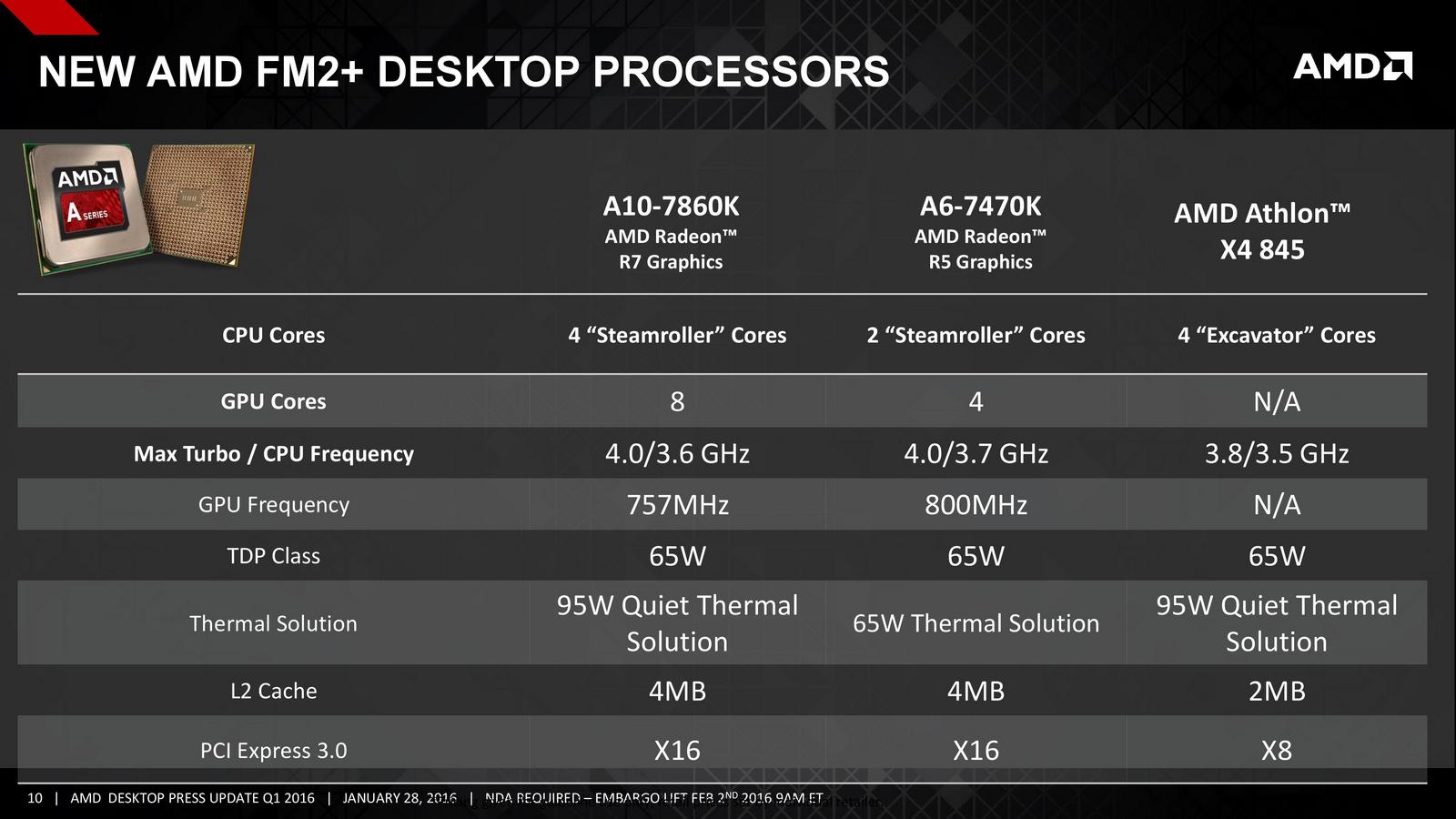

As part of today’s launch AMD released two new Kaveri based APUs as part of the FM2+ platform, the A10-7860K and the A6-7470K, as well as clarifying the way the new 125W Wraith stock cooler would be distributed at this time. What went under the radar almost was the release of a third part, the Athlon X4 845 CPU, featuring no integrated graphics but AMD’s newest architecture instead.

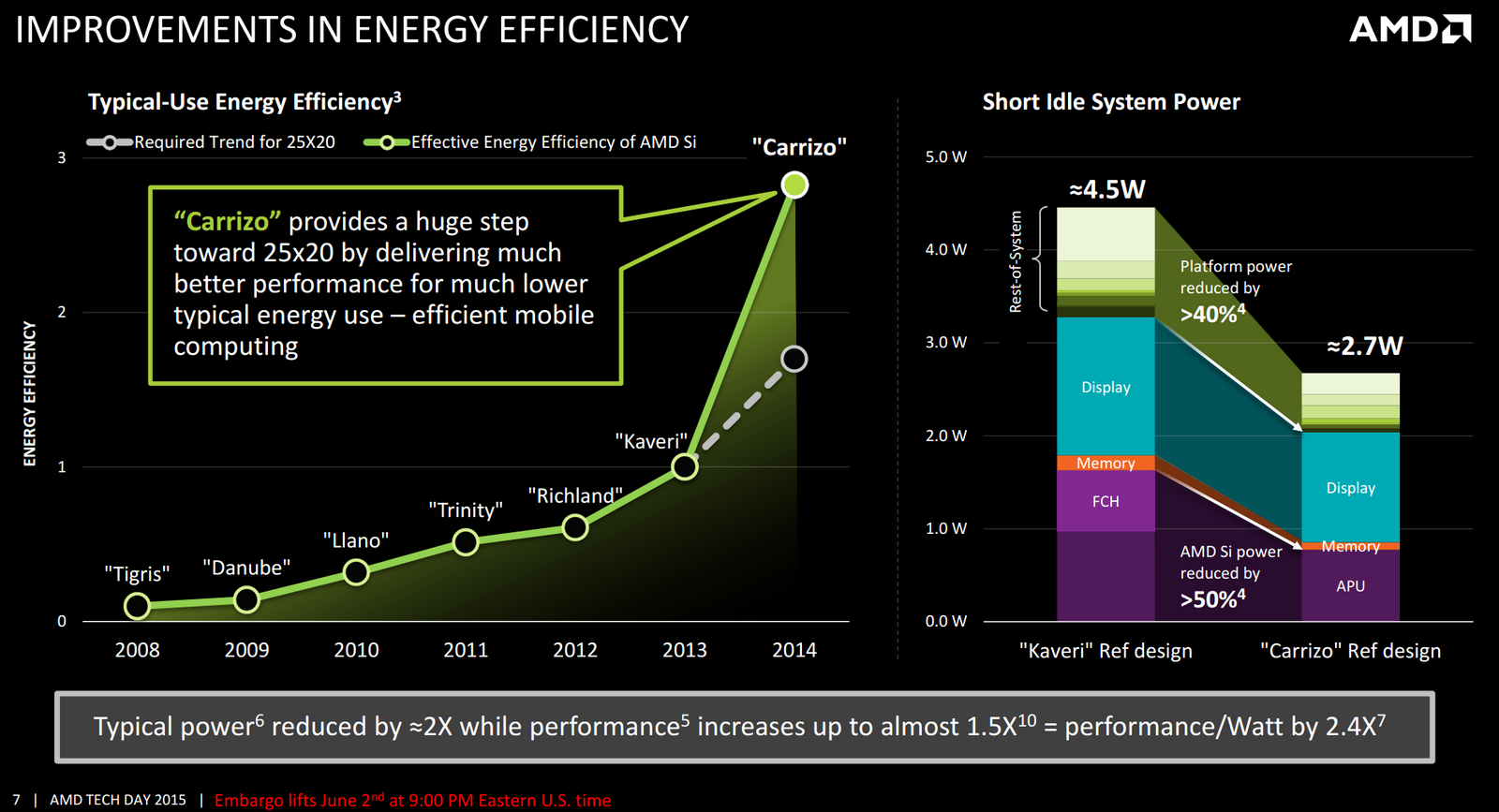

This makes good timing, because our review of AMD’s Carrizo, the mobile platform using the latest AMD architecture is set to go up in the next couple of days. AMD’s Excavator cores were the poignant part of AMD’s Tech Day in mid-2015, where the new Excavator architecture was discussed and especially in relation to the previous generation Steamroller cores.

The goal of Excavator, as we were told at the time, was to develop a series of big steps into improving the efficiency of the base Bulldozer microarchitecture through high density libraries, better metal stacks in production, more on-chip analysis to save power, more power planes to regulate those chances and everything in-between. We were told we wouldn’t see the Excavator core on the desktop in its desktop form because the design focused on the 15W-35W power window, rather than the 45W+ on the desktop.

Fast forward to today and there seems to be a slight reversal here. The new AMD Athlon X4 845 is a pair of Excavator modules in a desktop package, designed to slot right in where the Steamroller design through Kaveri has been sitting for a couple of years. Why the change? And why a single SKU at 65W, way off the 15W-35W range quoted as ‘ideal’ back at the Tech Day?

| AMD Excavator Based Lineup | ||||||

| A12 PRO- 8800B |

FX- 8800P |

A10- 8700P |

A8- 8600P |

A6-PRO 8500B |

Athlon X4 845 |

|

| Platform | Mobile | Mobile | Mobile | Mobile | Mobile | Desktop |

| Modules | 2 | 2 | 2 | 2 | 1 | 2 |

| Threads | 4 | 4 | 4 | 4 | 2 | 4 |

| Core Freq. (GHz) | 2.1-3.4 | 2.1-3.4 | 1.8-3.2 | 1.6-3.0 | 1.6-3.0 | 3.5-3.8 |

| Compute Units | 4+8 | 4+8 | 4+6 | 4+6 | 2+4 | 4+0 |

| Streaming Processors |

512 | 512 | 384 | 384 | 256 | N/A |

| IGP Freq. (MHz) | 800 | 800 | 800 | 720 | 800 | N/A |

| TDP | 15-35W | 15-35W | 15W | 15W | 15W | 65W |

| DRAM Frequency |

2133 | 2133 | 2133 | 2133 | 1600 | 2133 |

| L2 Cache | 2x1MB | 2x1MB | 2x1MB | 2x2MB | 2x1MB | 2x1MB |

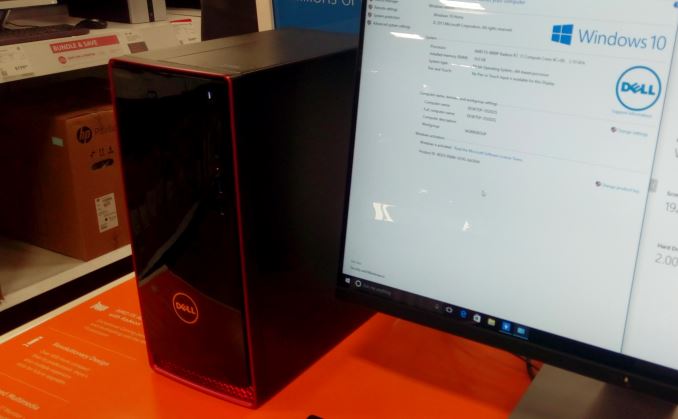

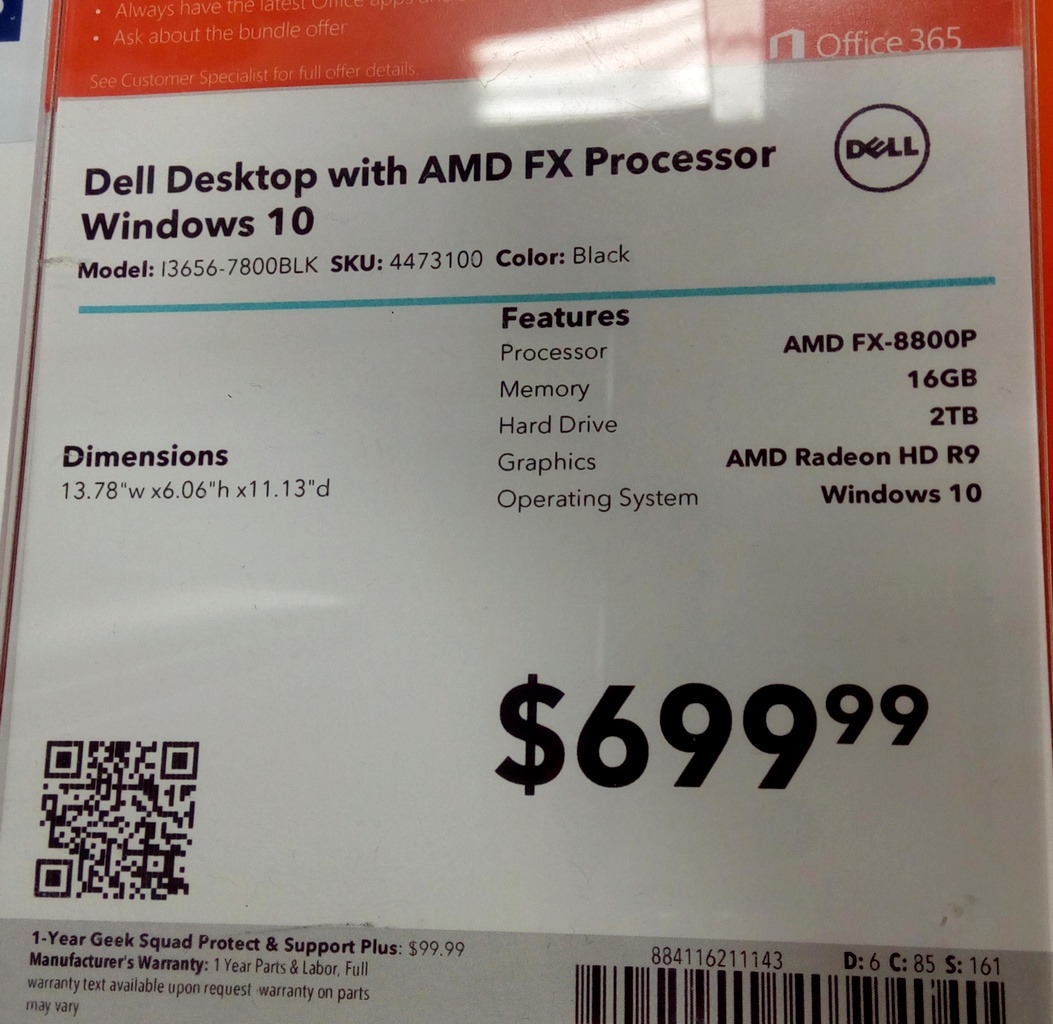

One thing that was made perfectly clear in AMD’s briefing on the new Athlon was that this is not a performance part – due to the nature of Excavator the new CPU would be purely an efficiency play, allowing customers to take advantage of the latest architecture in the desktop if they didn’t need the full-fat performance. Arguably you could already find Excavator in the desktop, through Dell’s Inspiron 3656 range which uses a mobile part in a desktop case with a discrete graphics card.

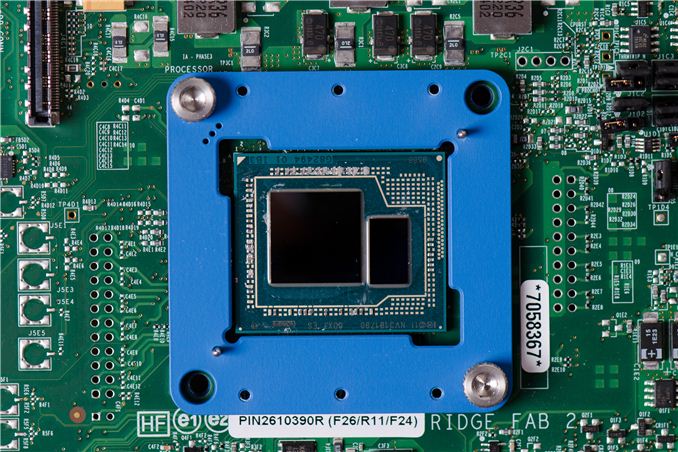

With the new Athlon, the fact that there is no graphics part to the FM2+ processor does raise several questions. Is this a new die specifically for the Excavator on desktop, which might run into the tens of millions of dollars to produce, or is it repurposed mobile silicon put into a desktop package. Instinct tells us it’s the latter, perhaps better binned parts to show that the core can do 3.8 GHz at 65W, but at the expense of the integrated graphics, or due to production issues the integrated graphics on die are unusable. One of the interesting things is also the L2 cache situation, because the Excavator modules in Carrizo were designed with 1MB of L2 per module, rather than the 2MB of L2 cache per module in desktop Kaveri. This is somewhat balanced by the larger L1 data cache in Excavator, but because there is no L3 cache either, it has to rely on other Excavator enhancements (better prefetch, wider prefetch windows) in order to bring it up to speed.

The PCIe 3.0 lanes are also at x8, which is another mobile limitation rather than the result of the PCIe root complex being half-disabled.

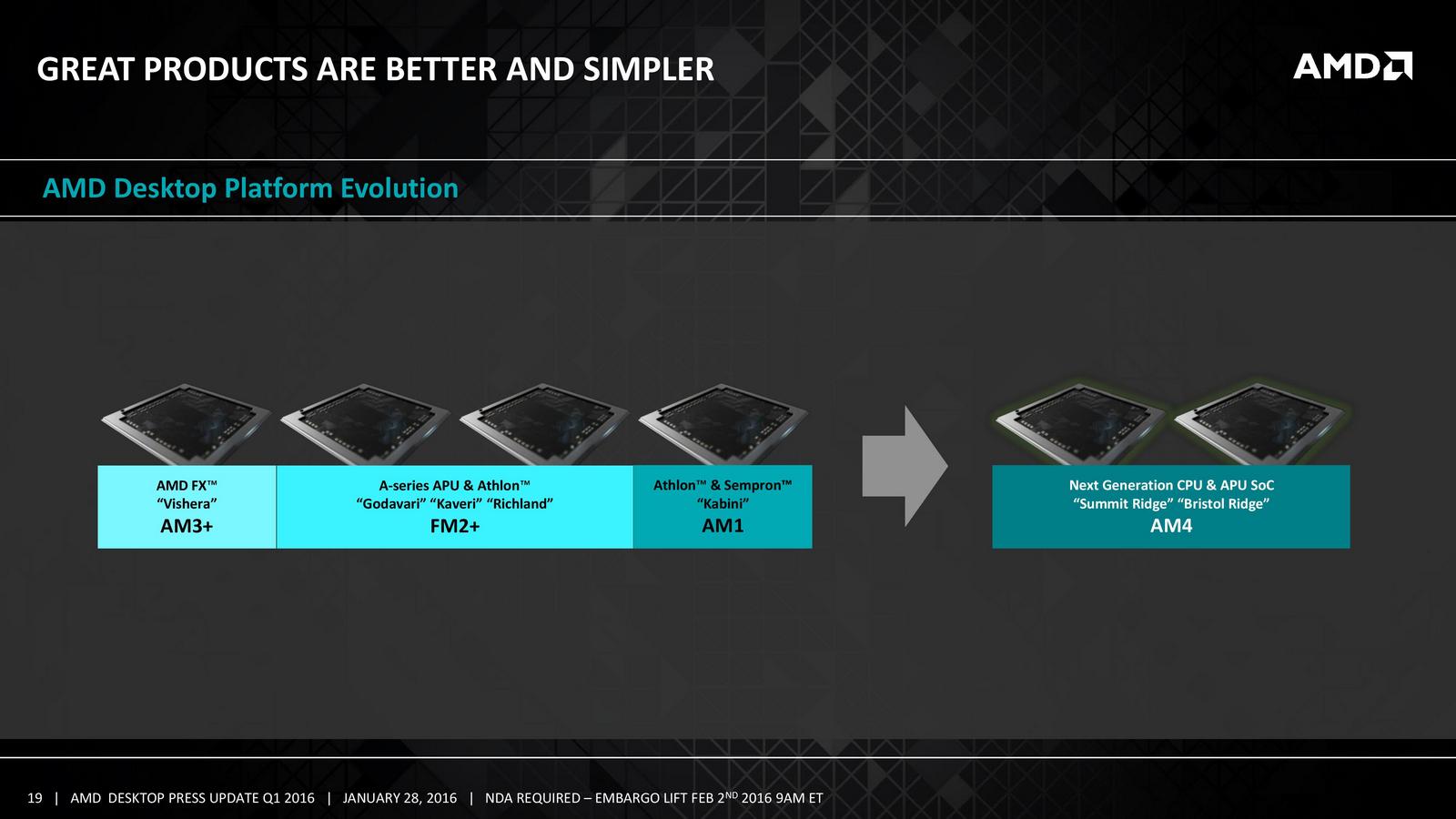

AMD has already stated that the next generation of AMD APUs will be on the AM4 platform, code named Bristol Ridge and Summit Ridge. We assume Bristol Ridge to be Excavator based, because there has to be something between now and Zen, but it would seem to suggest that the Excavator memory controller has support for DDR3 and DDR4, similar to what was suggested when AMD announced their DDR4-capable R-series APUs for embedded late last year. This may mean that AM4 supports both DDR3 and DDR4 as a result, which would not be unsurprising given how most DRAM transitions go.

We have asked for samples when they start to circulate. The Athlon X4 845 will have a MSRP of $70.

Source: AMD

Additional, 3rd Feb: We have been told by AMD that ‘The Athlon X4 845 is based on the “Carrizo” die with the GPU and FCH disabled. [T]he Athlon X4 845 supports DDR3 memory at speeds up to 2133MHz.’. Also, despite the focus on efficiency, the X4 845 will not have a configurable TDP.